Z80 ASSEMBLY LANGUAGE PROGRAMMING MANUAL

Copyright© 1977 by Zilog, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Zilog.

Zilog assumes no responsibility for the use of any circuitry other than circuitry embodied in a Zilog product. No other circuit patent licenses are implied.

## TABLE OF CONTENTS

|         | P.A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GE |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| I.      | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1  |

| II.     | SPECIFICATION OF Z80 ASSEMBLY LANGUAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|         | A. THE ASSEMBLY LANGUAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|         | B. OPERANDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4  |

|         | or model for walling modeling of order of the man, or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7  |

|         | E. ASSEMBLER COMMANDS 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3  |

| III.    | MACROS 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5  |

| IV.     | SUBROUTINES 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8  |

| V .     | Z80 CPU FLAGS 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0  |

| VI.     | Z80 INSTRUCTION SET 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •  |

|         | INSTRUCTION INDEX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5  |

| APPENDI | X:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|         | A. ERROR MESSAGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ^  |

|         | C. INSTRUCTION SORT LISTING (ALPHABETICAL) 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|         | The manual control of the control of | •  |

JANUARY 1978

#### Z80 ASSEMBLY LANGUAGE PROGRAMMING MANUAL

### INTRODUCTION:

The assembly language provides a means for writing a program without having to be concerned with actual memory addresses or machine instruction formats. It allows the use of symbolic addresses to identify memory locations and mnemonic codes (opcodes and operands) to represent the instructions themselves. Labels (symbols) can be assigned to a particular instruction step in a source program to identify that step as an entry point for use in subsequent instructions. Operands following each instruction represent storage locations, registers, or constant values. The assembly language also includes assembler directives that supplement the machine instruction. A pseudo-op, for example, is a statement which is not translated into a machine instruction, but rather is interpreted as a directive that controls the assembly process.

A program written in assembly language is called a source program. It consists of symbolic commands called statements. Each statement is written on a single line and may consist of from one to four entries: A label field, an operation field, an operand field and a comment field. The source program is processed by the assembler to obtain a machine language program (object program) that can be executed directly by the Z80-CPU.

Zilog provides several different assemblers which differ in the features offered. Both absolute and relocatable assemblers are available with the Development and Microcomputer Systems. The absolute assembler is contained in base level software operating in a 16K memory space while the relocating assembler is part of the RIO environment operating in a 32K memory space.

#### II SPECIFICATION OF THE Z80 ASSEMBLY LANGUAGE

#### A. THE ASSEMBLY LANGUAGE

The assembly language of the Z80 is designed to minimize the number of different opcodes corresponding to the set of basic machine operations and to provide for a consistent description of instruction operands. The nomenclature has been defined with special emphasis on mnemonic value and readability.

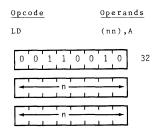

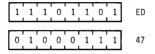

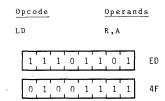

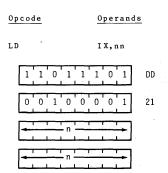

The movement of data is indicated primarily by a single opcode, LD for example, regardless of whether the movement is between different registers or between registers and memory locations.

The first operand of an LD instruction is the destination of the operation, and the second operand is the source of the operation. For example:

#### LD A.B

indicates that the contents of the second operand, register B, are to be transferred to the first operand, register A. Similarly,

#### LD C, 3FH

indicates that the constant 3FH is to be loaded into the register C. In addition, enclosing an operand wholly in parentheses indicates a memory location addressed by the contents of the parentheses. For example,

#### LD HL, (1200)

indicates the contents of memory locations 1200 and 1201 are to be loaded into the 16-bit register pair HL. Similarly,

#### LD (IX+6),C

indicates the contents of the register C are to be stored in the memory location addressed by the current value of the 16-bit index register IX plus 6.

The regular formation of assembly instructions minimizes the number of mnemonics and format rules that the user must learn and manipulate.

Additionally, the resulting programs are easier to interpret which in turn reduces programming errors and improves the maintainability of the software.

#### B. OPERANDS

Operands modify the opcodes and provide the information needed by the assembler to perform the designated operation.

Certain symbolic names are reserved as key words in the assembly language operand fields. They are:

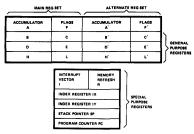

- The contents of 8-bit registers are specified by the character corresponding to the register names. The register names are A,B,C,D,E,H,L,I,R.

- 2) The contents of 16-bit double registers and register pairs consisting of two 8-bit registers are specified by the two characters corresponding to the register name or register pair. The names of double registers are IX, IY and SP. The names of registers pairs are AF, BC, DE and HL.

- 3) The contents of the auxiliary register pairs consisting of two 8-bit registers are specified by the two characters corresponding to the register pair names followed by an apostrophe. The auxiliary register pair names are AF', BC', DE' and HL'. Only the pair AF' is actually allowed as an operand, and then only in the EX AF, AF' instruction.

- 4) The state of the four testable flags is specified as follows:

| ON CONDITION | OFF                 |

|--------------|---------------------|

|              |                     |

| С            | NC                  |

| z            | NZ                  |

| M (minus)    | P (plus)            |

| PE (even)    | PO (odd)            |

|              | C<br>Z<br>M (minus) |

#### OPERAND NOTATION

The following notation is used in the description of the assembly language:

- r specifies any one of the following registers: A,B,C,D,E,H,L.

- (HL) specifies the contents of memory at the location addressed by the contents of the register pair HL.

- n specifies a one-byte expression in the range (0 to 255) nn specifies a two-byte expression in the range (0 to 65535).

- 4) d specifies a one-byte expression in the range (-128,127).

- 5) (nn) specifies the contents of memory at the location addressed by the two-byte expression nn.

- 6) b specifies an expression in the range (0,7).

- 7) e specifies a one-byte expression in the range (-126,129).

- cc specifies the state of the Flags for conditional JR, JP, CALL and RET instructions.

- qq specifies any one of the register pairs BC, DE, HL or AF.

- 10) ss specifies any one of the following register pairs: BC,DE,HL,SP.

- pp specifies any one of the following register pairs: BC,DE,IX,SP.

- 12) rr specifies any one of the following register pairs: BC,DE,IY,SP.

- 13) s specifies any of r,n,(HL),(IX+d),(IY+d).

- 14) dd specifies any one of the following register pairs: BC,DE,HL,SP.

- 15) m specifies any of r, (HL), (IX+d), (IY+d).

#### C. RULES FOR WRITING ASSEMBLY STATEMENTS (SYNTAX)

An assembly language program (source program) consists of labels, opcodes, operands, comments and pseudo-ops in a sequence which defines the user's program.

There are 74 generic opcodes (such as LD), 25 operand key words (such as A), and 694 legitimate combinations of opcodes and operands in the Z80 instruction set.

#### ASSEMBLER STATEMENT FORMAT:

Statements are always written in a particular format. A typical Assembler statement is shown below:

LABEL OPCODE OPERANDS COMMENT LOOP: LD HL.VALUE :GET VALUE

In this example, the label, LOOP, provides a means for assigning a specific name to the instruction LOAD (LD), and is used to address the statement in other statements. The operand field contains one or two entries separated by one or more commas, tabs or spaces. The comment field is used by the programmer to quickly identify the action defined by the statement. Comments must begin with a semicolon and labels must be terminated by a colon, unless the label starts in column No. 1.

#### D ASSEMBLY LANGUAGE CONVENTIONS

#### LABELS

A label is a symbol representing up to 16 bits of information and is used to specify an address or data. By using labels effectively, the user can write assembly language programs more rapidly and make fewer errors. If the programmer attempts to use a symbol that has been defined as greater than 8 bits for an 8-bit data constant, the assembler will generate an error message.

A label is composed of a string of one or more characters, of which the first six must be unique. For example, the labels 'longname' and 'longnamealso' will be considered to be the same label. The first character must be alphabetic and any following characters must be either alphanumeric, the question mark (?) or the under bar character (\_). Any other characters within a label will cause an error. A label can start in any column if immediately followed by a colon. It does not require a colon if started in column one.

The assembler maintains a location counter to provide addresses for the symbols in the label field. When a symbol is found in the label field, the assembler places the symbol and the corresponding location counter value in a symbol table.

The symbol table normally resides in RAM, but it will automatically overflow to disk, so there is no limit to the number of labels that can be processed.

#### EXPRESSIONS

An expression is an operand entry consisting of either a single term (unary) or a combination of terms (binary). It contains a valid series of constants, variables and functions that can be connected by operation symbols. The Z80 Assembler will accept a wide range of expressions involving arithmetic and logical operations. The assembler will evaluate all expressions from left to right in the order indicated in the table below:

| OPERATOR   | FUNCTION             | PRIORITY |

|------------|----------------------|----------|

| +          | UNARY PLUS           | 1        |

| _          | UNARY HINUS          | 1        |

| .NOT. or \ | LOGICAL NOT          | 1        |

| .RES.      | RESULT               | 1        |

| **         | EXPONENTIATION       | 2        |

| *          | MULTIPLICATION       | 3        |

| /          | DIVISION             | 3        |

| .110D.     | MODULO               | 3        |

| .SHR.      | LOGICAL SHIFT RIGHT  | 3        |

| .SHL.      | LOGICAL SHIFT LEFT   | 3        |

| +          | ADDITION             | 4        |

| -          | SUBTRACTION          | 4        |

| .AND. or & | LOGICAL AND          | 5        |

| .OR. or ↑  | LOGICAL OR           | 6        |

| .XOR.      | LOGICAL XOR          | 6        |

| .EQ. or =  | EQUALS               | 7        |

| .GT. or >  | GREATER THAN         | 7        |

| .LT. or <  | LESS THAN            | 7        |

| .UGT.      | UNSIGNED GREATER THA | AN 7     |

| .ULT.      | UNSIGNED LESS THAN   | 7        |

Parenthesis can be used to ensure correct expression evaluation. Note, however, that enclosing an expression wholly in parenthesis indicates a memory address.

Delimiters such as spaces or commas are not allowed within an expression since they serve to separate the expression from other portions of the statement.

16-bit integer arithmetic is used throughout.

Note that the negative of an expression can be formed by a preceding minus sign -. For example:

LD HL, -OEA9H.

The five comparison operators (.EQ., .GT., .LT., .UGT. and .ULT.) will evaluate to a logical True (all ones) if the comparison is true logical False (zero) otherwise. The operators .GT. and .LT. deal with signed numbers whereas .UGT. and .ULT. assume unsigned arguments.

The Result operator (.RES.) causes overflow to be

suppressed during evaluation of its argument, thus overflow is not flagged with an error message.

For example:

LD BC, 7FFFH+1 would cause an error message, whereas LD BC, RES, (7FFFH+1) would not.

The Modulo operator (.MOD.) is defined as:

X,MOD,Y = X-Y\*(X/Y) where the division (X/Y) is integer division.

The Shift operator (.SHR.,.SHL.) shifts the first argument right or left by the number of positions given in the second argument. Zeros are shifted into the high-order or low-order bits, respectively.

In specifying relative addressing with either the JR (Jump Relative) or DJNZ (Decrement and Jump if Not Zero) instructions, the Assembler automatically subtracts the value of the next instruction's reference counter from the value given in the operand field to form the relative address for the jump instruction. For example:

JR C.LOOP

will jump relative to the instruction labeled LOOP if the Carry flag is set. The limits on the range of a relative address is 128 bytes in either direction from the reference counter of the next instruction. An error message will be generated if this range is exceeded.

The symbol \$ is used to represent the value of the reference counter of the current instruction, and can be used in general expressions. An expression which evaluates to a displacement in the range <-126,+129> can be added to the reference counter to form a relative address. For example:

JR C, \$+5

will jump relative to the instruction which is 5 bytes beyond the current instruction.

#### PSEUDO-OPS (ASSEMBLER DIRECTIVES)

There are several pseudo-ops which the various Zilog assemblers will recognize. These assembler directives, although written much like processor instructions, are commands to the assembler instead of to the processor. They direct the assembler to perform specific tasks during the assembly process but have no meaning to the Z80 processor. These assembler pseudo-ops are:

- ORG nn Sets address reference counter to

- EQU nn Sets value of a label to nn in the program: can occur only once for any label.

- DEFL nn Sets value of a label to nn and can be repeated in the program with different values for the same label.

- END Signifies the end of the source program so that any following statement will be ignored. If there is no end statement, then the end-of-file mark in the last source file will designate the end of the source program.

- DEFB n Defines the contents of a byte at the current reference counter to be

- DEFB 's' Defines the content of one byte of memory to be the ASCII representation of character s.

- DEFW nn Defines the contents of a two-byte word to be nn. The least significant byte is located at the current reference counter while the most significant byte is located at the reference counter plus one.

- DEFS nn Reserves nn bytes of memory starting at the current value of the reference counter.

DEFII 's' Defines the content of n bytes of memory to be the ASCII representation of string s, where n is the length of s and must be in the range 0<=n<=63.

MACRO #Po #Pl...#Pn Declares the label to be a macro name with formal parameters Po through Pn.

Subsequent statements define the body of the macro.

ENDM Marks the end of a macro definition.

Pseudo-ops are assembled exactly like executable instructions, and may be preceded by a label and followed by a comment. (The label is required for EQU, DEFL and MACR pseudo-ops.) In the above pseudo-op definitions, the reference counter corresponds to the program counter and is used to assign and calculate machine-language addresses for the object file.

#### CONDITIONAL PSEUDO-OPS

Conditional pseudo-ops provide the programmer with the capability to conditionally include or not include portions of his source code in the assembly process. Conditional pseudo-ops are:

COND nn Evaluates expression nn. If the expression is true (non-zero), the COND pseudo-op is ignored. If the expression is false (zero), the assembly of subsequent statements is disabled. COND pseudo-ops cannot be nested.

ENDC Re-enables assembly of subsequent statements.

#### DELIMITERS

A delimiter is used to specify the bounds of a certain related group of characters in a source program. The delimiters recognized by the assembler are commas or spaces. A delimiter cannot

occur within an expression.

#### COMMENTS

Comments are not a functional part of an assembly program, but instead are used for program documentation to add clarity, and to facilitate software maintenance. A comment is defined as any string following a semicolon in a line, and is ignored by the assembler. Comments can begin in any column.

#### I/O BUFFERS

The Z80 Assembler uses a buffered I/O technique for handling the assembly language source file, listing file, object file and temporary files. The assembler automatically determines the available work space and allocates the buffer sizes accordingly. Hence there are no constraints on the size of the assembly language source file that can be assembled.

#### UPPER/LOWER CASE

The assembler processes source text which contains both upper and lower case alphabetic characters in the following manner. All opcodes and keywords, such as register names or condition codes, must be either all capitals or all lower case. Label names may consist of any permutation of upper and lower case, however, two names which differ in case will be treated as two different names. Thus, LABEL, label and LaBel will be considered as three different names. Notice that one could use a mixture of case to allow definition of labels or macros which look similar to opcodes, such as Push or LdiR, without redefining the meaning of the opcode. All assembler commands, such as \*List or \*Include (see below) can be in either upper or lower case, as can arithmetic operators such as NOT.,.AND. or .EQ., and numbers can be any mixture of case, such as Offffh, OAbCdH or O11001b.

#### NUMBER BASES

The Assembler will accept numbers in several

different bases: binary, octal, decimal and hexadecimal. Numbers must always start with a digit (leading zeros are sufficient), and may be followed immediately by a single letter which signifies the base of the number ('B' for binary, 'O' or 'Q' for octal, 'D' for decimal and 'H' for hexadecimal). If no base is specified decimal is assumed. For example, the same number is represented in each of the four bases:

1011100B, 134Q, 1340, 92, 92D, 05CH

#### E. ASSEMBLER COMMANDS

The Z80 Assembler recognizes several commands to modify the listing format. An assembler command is a line of the source file beginning with an \* in column one. The character in column two identifies the type of command. Arguments, if any, are separated from the command by any number of blanks or commas. The following commands are recognized by the assembler:

| *Eject            | Causes the listing to advance to a new page starting with this line.                                                                                                                                           |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *Heading s        | Causes string s to be taken as a heading to be printed at the top of each new page. Strings s may be any string of zero to 28 characters, not containing leading blanks. This command does an automatic Eject. |

| *List OFF         | Causes listing and printing to be suspended, starting with this line.                                                                                                                                          |

| *List ON          | Causes listing and printing to resume, starting with this line.                                                                                                                                                |

| *Maclist OFF      | Causes listing and printing of macro expansions to be suspended, starting with this line.                                                                                                                      |

| *Maclist ON       | Causes listing and printing of macro expansions to resume, starting with this line.                                                                                                                            |

| *Include filename | Causes the source file filename to be included in the source stream                                                                                                                                            |

following the command statement.

The expected use of \*Include is for files of macro definitions, lists of EQUates, or commonly used subroutines, although it can be used anywhere in a program that the other commands would be legal. The filename must follow the normal convention for specifying filenames, and furthermore only file types 'F' through 'T' are allowed. The default type is 'S'. The included file may also contain a \*Include command, up to a nested level of four,

\*Include will always try to shoe-horn the file in inside a macro definition, and although the \*Include statement will appear in a macro expansion, the file will not be included again at the point of expansion. \*Include works in the expected manner in conjunction with conditional assembly.

For example:

COND exp

\*Include FILE1

ENDC

;FILE1 is included only if the value of exp is non-zero.

#### III. MACROS

Macros provide a means for the user to define his own opcodes, or to redefine existing opcodes. A macro defines a body of text which will be automatically inserted in the source stream at each occurrence of a macro call. In addition, parameters provide a capability for making limited changes in the macro at each call.

If a macro is used to redefine an existing opcode, a warning message is generated to indicate that future use of that opcode will always be processed as a macro call. If a program uses macros, then the asembly option M must be specified.

#### MACRO DEFINITION

The body of text to be used as a macro is given in the macro definition. Each definition begins with a MACRO statement and end with an ENDM statement. The general forms are:

<name> MACRO [#<PO>, #<P1>,...,#<Pn>]

[<label>] ENDM

The label <name> is required, and must obey all the usual rules for forming labels. The quantity in brackets is an optional set of parameters.

There can be any number of parameters, each starting with the symbol #. The rest of the parameter name can be any string not containing a delimiter (blank, comma, semicolon) or the symbol #. However, parameters will be scanned left to right for a match, so the user is cautioned not to use parameter names which are prefix substrings of later parameter names. Parameter names are not entered in the symbol table.

The label on an ENDM is optional, but if one is given it must obey all the usual rules for forming labels.

Each statement between the MACRO and ENDM statements is entered into a temporary macro file. The only restriction on these statements is that they do not include another macro definition. (Nested definitions are not allowed.) They may

include macro calls. (Recursion is allowed.)

The statements of the macro body are not assembled at definition time, so they will not define labels, generate code, or cause errors. Exceptions are the assembler commands such as \*List, which are executed wherever they occur. Within the macro body text, the formal parameter names may occur anywhere that an expansion-time substitution is desired. This includes comments and quoted strings. The symbol # may not occur except as the first symbol of a parameter name.

Macros must be defined before they are called.

#### MACRO CALLS AND MACRO EXPANSION

A macro is called by using its name as an opcode at any point after the definition. The general form is:

[<label>] <name> ['<\$0>','<\$1>',...,'\$n>']

The <label> is optional, and <name> must be a previously defined macro. There may be any number of argument strings, <Sn>, separated by any number of blanks or commas. Commas do not serve as parameter place holders, only as string delimeters. If there are too few parameters, the missing ones are assumed to be null. If there are too many, the extras are ignored. The position of each string in the list corresponds with the position of the macro parameter name it is to replace. Thus, the third string in a macro call statement will be substituted for each occurrence of the third parameter name.

The strings may be of any length and may contain any characters. The outer level quotes around the string are generally optional, but are required if the string contains delimiters or the quote character itself. The quote character is represented by two successive quote marks at the inner level. The outer level quotes, if present, will not occur in the substitution. The null string, represented by two successive quote marks at the outer level, may be used in any parameter position.

After processing the macro call statement, the assembler switches its input from the source file

to the macro file. Each statement of the macro body is scanned for occurrences of parameter names, and for each occurrence found, the corresponding string from the macro call statement is substituted. After substitution, the statement is assembled normally.

#### SYMBOL GENERATOR

Every macro definition has an implicit parameter named #\$YM. This may be referenced by the user in the macro body, but should not explicitly appear in the IACRO statement. At expansion time, each occurrence of #\$YM in the definition is replaced by a string representing a 4-digit hexadecimal constant.

This string is constant over a given level of macro expansion, but increases by one for each new macro call. The most common use of #\$YH is to provide unigue labels for different expansion of the same macro. Otherwise, a macro containing a label would cause multiple definition errors if it were called more than once.

#### LISTING FORMAT

By default, each expanded statement is listed with a blank STMT field. If the Maclist flag is turned off by the NOM option or \*M OFF, then only the macro call is listed.

#### IV. SUBROUTINES

Subroutines are blocks of instructions that can be called during the execution of a sequence of instructions. Subroutines can be called from main programs or from other subroutines. A subroutine is entered by the CALL opcode as in:

#### CALL REWIND

Parameters such as those used by the macros are not used with subroutines. When a call instruction is encountered during execution of a program, the PC is changed to the first instruction of the subroutine. The subsequent address of the invoking program is pushed on the stack. Control will return to this point when the subroutine is finished. The processor continues to execute the subroutine until it encounters a RET (return) instruction. At this point the return address is popped off the stack into the PC, and the processor returns to the address of the instruction following the CALL to continue execution from that point.

Subroutines of any size can be invoked from programs or other subroutines of any size, without restriction. Care must be taken when nesting subroutines (subroutines within subroutines) that pushes and pops remain balanced at each level. If the processor encounters a RET with an un-popped push on the stack, the PC will be set to a meaningless address rather than to the next instruction following the CALL.

Tradeoffs must be considered between:

- a) using a block of code repetitively in line, and

- calling the block repetitively as a subroutine.

Program size can usually be saved by using the subroutine. If the repetitive block contains N bytes and it is repeated on N occasions in the program,

- a) MxN bytes would be used in direct programming, while

- b) 3M (for CALLS)

- + N (for the block)

- + 1 (for the RET)

- = 3M+N+1 bytes would be required if using a subroutine.

For example, for a block of 20 bytes used 5 times, in-line programming would require 100 bytes while a subroutine would require 36.

An added advantage of subroutines is that with careful naming, program structures become clearer, easter to read and easier to debug and maintain. Subroutines written for one purpose can be employed elsewhere in other programs requiring the same function.

Subroutines differ from Macros in several ways:

- a) Subroutine code is assembled into an object program only once although it may be called many times. Macro code is assembled in line every place the macro is used.

- b) Registers and pointers required by a subroutine must be set up before the CALL. No parameters are used and no argument string can be issued. Macros, through their use of parameters, can modify the settings of registers on each occurrence.

#### V. Z80 STATUS INDICATORS (FLAGS)

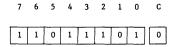

The flag register (F and F') supplies information to the user regarding the status of the Z80 at any given time. The bit positions for each flag is shown below:

|   | 7 | 6 | 5 | 4 | 3 | 2   | 1 | 0 |  |

|---|---|---|---|---|---|-----|---|---|--|

| - | S | z | Х | Н | X | P/V | N | С |  |

#### WHERE:

C = CARRY FLAG

N = ADD/SUBTRACT FLAG

P/V = PARITY/OVERFLOW FLAG

H = HALF-CARRY FLAG

Z = ZERO FLAG

S = SIGN FLAG

X = NOT USED

Each of the two Z-80 Flag Registers contains 6 bits of status information which are set or reset by CPU operations. (Bits 3 and 5 are not used.) Four of these bits are testable (C,P/V,Z and S) for use with conditional jump, call or return instructions. Two flags are not testable (H,N) and are used for BCD arithmetic.

#### CARRY FLAG (C)

The carry bit is set or reset depending on the operation being performed. For 'ADD' instructions that generate a carry and 'SUBTRACT' instructions that generate a borrow, the Carry Flag will be set. The Carry Flag is reset by an ADD that does not generate a carry and a 'SUBTRACT' that generates no borrow. This saved carry facilitates software routines for extended precision arithmetic. Also, the "DAA" instruction will set the Carry Flag if the conditions for making the decimal adjustment are met.

For instructions RLA, RRA, RLS and RRS, the carry bit is used as a link between the LSB and MSB for any register or memory location. During instructions RLCA, RLC s and SLA s, the carry contains the last value shifted out of bit 7 of any register or memory location. During

instructions RRCA, RRC s, SRA s and SRL s the carry contains the last value shifted out of bit 0 of any register or memory location.

For the logical instructions AND s, OR s and XOR s, the carry will be reset.

The Carry Flag can also be set (SCF) and complemented (CCF).

#### ADD/SUBTRACT FLAG (N)

This flag is used by the decimal adjust accumulator instruction (DAA) to distinguish between 'ADD' and 'SUBTRACT' instructions. For all 'ADD' instructions, N will be set to an 'O'. For all 'SUBTRACT' instructions, N will be set to a '1'.

#### PARITY/OVERFLOW FLAG

This flag is set to a particular state depending on the operation being performed.

For arithmetic operations, this flag indicates an overflow condition when the result in the Accumulator is greater than the maximum possible number (+127) or is less than the minimum possible number (-128). This overflow condition can be determined by examining the sign bits of the operands.

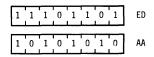

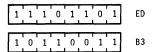

For addition, operands with different signs will never cause overflow. When adding operands with like signs and the result has a different sign, the overflow flag is set. For example:

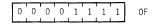

| +120 | = | 0111 | 1000 | ADDEND    |

|------|---|------|------|-----------|

| +105 | = | 0110 | 1001 | AUGEND    |

| +225 |   | 1110 | 0001 | (-95) SUM |

The two numbers added together has resulted in a number that exceeds +127 and the two positive operands has resulted in a negative number (-95) which is incorrect. The overflow flag is therefore set.

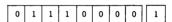

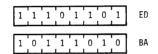

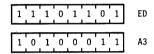

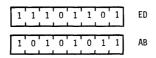

For subtraction, overflow can occur for operands of unlike signs. Operands of like sign will never cause overflow. For example:

| +127      | 0111 | 1111 | MINUEND    |

|-----------|------|------|------------|

| (-) $-64$ | 1100 | 0000 | SUBTRAHEND |

| +191      | 1011 | 1111 | DIFFERENCE |

The minuend sign has changed from a positive to a negative, giving an incorrect difference. Overflow is therefore set.

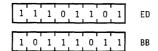

Another method for predicting an overflow is to observe the carry into and out of the sign bit. If there is a carry in and no carry out, or if there is no carry in and a carry out, then overflow has occurred.

This flag is also used with logical operations and rotate instructions to indicate the parity of the result. The number of 'l' bits in a byte are counted. If the total is odd, 'ODD' parity (P=0) is flagged. If the total is even, 'EVEN' parity is flagged (P=1).

During search instructions (CPI,CPIR,CPD,CPDR) and block transfer instructions (LDI,LDIR, LDD,LDDR) the P/V flag monitors the state of the byte count register (BC). When decrementing, the byte counter results in a zero value, the flag is reset to 0, otherwise the flag is a Logic 1.

During LD A,I and LD A,R instructions, the P/V flag will be set with the contents of the interrupt enable flip-flop (IFF2) for storage or testing.

When inputting a byte from an I/O device, IN r,(C), the flag will be adjusted to indicate the parity of the data.

#### THE HALF CARRY FLAG (H)

The Half Carry Flag (H) will be set or reset depending on the carry and borrow status between bits 3 and 4 of an 8-bit arithmetic operation. This flag is used by the decimal adjust accumulator instruction (DAA) to correct the result of a packed BCD add or subtract operation. The H flag will be set (1) or reset (0) according to the following table:

| H | ADD                                   | SUBTRACT                            |

|---|---------------------------------------|-------------------------------------|

| 1 | There is a carry from Bit 3 to Bit 4  | There is<br>borrow from<br>bit 4    |

| 0 | There is no carry from Bit 3 to Bit 4 | There is no<br>borrow from<br>Bit 4 |

#### THE ZERO FLAG (Z)

The Zero Flag (Z) is set or reset if the result generated by the execution of certain instructions is a zero.

For 8-bit arithmetic and logical operations, the Z flag will be set to a 'l' if the resulting byte in the Accumulator is zero. If the byte is not zero, the Z flag is reset to '0'.

For compare (search) instructions, the Z flag will be set to a 'l' if a comparison is found between the value in the Accumulator and the memory location pointed to by the contents of the register pair HL.

When testing a bit in a register or memory location, the Z flag will contain the complemented state of the indicated bit (see Bit b.s).

When inputting or outputting a byte between a memory location and an I/O device (INI;IND;OUTI and OUTD), if the result of B-1 is zero, the Z flag is set, otherwise it is reset. Also for byte inputs from I/O devices using IN r,(C), the Z Flag is set to indicate a zero byte input.

### THE SIGN FLAG (S)

The Sign Flag (S) stores the state of the most significant bit of the Accumulator (Bit 7). When the Z80 performs arithmetic operations on signed numbers, binary two's complement notation is used to represent and process numeric information. A positive number is identified by a '0' in bit 7. A negative number is identified by a '1'. The binary equivalent of the magnitude of a positive number is stored in bits 0 to 6 for a total range of from 0 to 127. A negative number is represented by the two's complement of the equivalent positive number. The total range for negative numbers is from -1 to -128.

When inputting a byte from an I/O device to a register, IN r,(C), the S flag will indicate either positive (S=0) or negative (S=1) data.

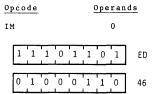

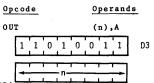

#### VI. Z80 INSTRUCTION SET

NOTE: Execution time (E.T.) for each instruction is given in nicroseconds for an assumed 4 MHZ clock. Total machine cycles (M) are indicated with total clock periods (T States). Also indicated are the number of T States for each M cycle. For example:

M CYCLES: 2 T STATES: 7(4.3) 4 MHZ E.T.: 1.75

indicates that the instruction consists of 2 machine cycles. The first cycle contains 4 clock periods (T States). The second cycle contains 3 clock periods for a total of 7 clock periods or T States. The instruction will execute in 1.75 microseconds.

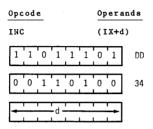

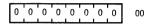

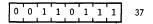

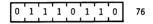

Register format is shown for each instruction with the most significant bit to the left and the least significant bit to the right.

## Z80 INSTRUCTION SET TABLE OF CONTENTS

|                                                    | PAGE |

|----------------------------------------------------|------|

| -8 BIT LOAD GROUP                                  | 26   |

| -16 BIT LOAD GROUP                                 | 52   |

| -EXCHANGE, BLOCK TRANSFER AND SEARCH GROUP         | 76   |

| -8 BIT ARITHMETIC AND LOGICAL GROUP                | 99   |

| -GENERAL PURPOSE ARITHMETIC AND CPU CONTROL GROUPS | 131  |

| -16 BIT ARITHMETIC GROUP                           | 146  |

| -ROTATE AND SHIFT GROUP                            | 163  |

| -BIT SET, RESET AND TEST GROUP                     | 202  |

| -JUMP GROUP                                        | 219  |

| -CALL AND RETURN GROUP                             | 237  |

| -INPUT AND OUTPUT GROUP                            | 252  |

| -INSTRUCTION INDEX                                 | 275  |

|                                       | 1 |

|---------------------------------------|---|

| e e e e e e e e e e e e e e e e e e e | 1 |

|                                       |   |

|                                       |   |

|                                       |   |

|                                       |   |

|                                       |   |

|                                       |   |

|                                       |   |

|                                       | 1 |

8 BIT LOAD GROUP

## \_D r, r'

Operation:  $r \leftarrow r'$

#### Format:

| Opcode  | Operands |

|---------|----------|

| LD      | r,r'     |

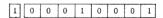

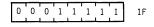

| 0 1 - r | - r -    |

#### Description:

The contents of any register r' are loaded into any other register r. Note: r,r' identifies any of the registers A, B, C, D, E, H, or L, assembled as follows in the object code:

| Register |   | <u>r,r</u> |

|----------|---|------------|

| A        | = | 111        |

| В        | = | 000        |

| C        | = | 001        |

| D        | - | 010        |

| E        | - | 011        |

| н        | _ | 100        |

| L        | = | 101        |

M CYCLES: 1 T STATES: 4 4 MHZ E.T.: 1.0

Condition Bits Affected: None

## Example:

If the H register contains the number 8AH, and the E register contains 10H, the instruction

LD H. E

would result in both registers containing 10H.

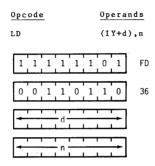

## Operation: $r \leftarrow n$

#### Format:

| Opcode                                     | Operands |

|--------------------------------------------|----------|

| LD                                         | r, n     |

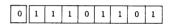

| $0  0 \longrightarrow r \longrightarrow 1$ | 1 0      |

| <u> </u>                                   |          |

## Description:

The eight-bit integer n is loaded into any register r, where r identifies register A, B, C, D, E, H or L, assembled as follows in the object code:

## Register

A = 111

B = 000

C = 001

D = 010

E = 011

H = 100

L = 101

M CYCLES: 2

T STATES: 7(4,3) 4 MHZ E.T.: 1.75

Condition Bits Affected: None

## Example:

After the execution of

LD E, A5H

the contents of register E will be A5H.

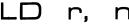

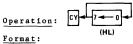

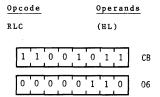

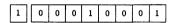

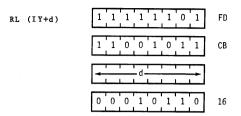

Operation:  $r \leftarrow (HL)$

## Format:

| Opcode             | Op  | Operands |  |

|--------------------|-----|----------|--|

| LD                 | r,  | (HL)     |  |

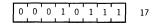

| 0 1 <del>- r</del> | 1 1 | 0        |  |

## Description:

The eight-bit contents of memory location (HL) are loaded into register r, where r identifies register A, B, C, D, E, H or L, assembled as follows in the object code:

## Register A = 111B = 000

C = 001

D = 010E = 011H = 100

L = 101

M CYCLES: 2 T STATES: 7(4,3) 4 MHZ E.T.: 1.75

Condition Bits Affected: None

## Example:

If register pair HL contains the number 75AlH, and memory address 75AlH contains the byte 58H, the execution of

LD C, (HL)

will result in 58H in register C.

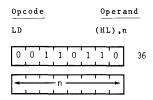

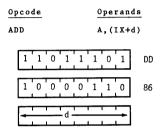

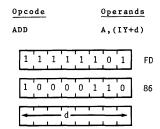

# LD r, (IX+d)

Operation:  $r \leftarrow (IX+d)$

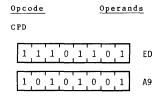

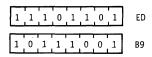

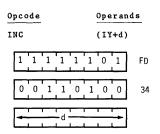

#### Format:

| <u>Opcode</u>                              | Operands  |

|--------------------------------------------|-----------|

| LD                                         | r, (IX+d) |

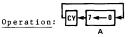

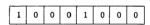

| 1 1 0 1 1 1                                | 0 1 DD    |

|                                            | <u> </u>  |

| $0  1 \longrightarrow r \longrightarrow 1$ | 1 0       |

| <b>←</b> d                                 |           |

|                                            |           |

### Description:

The operand (IX+d) (the contents of the Index Register IX summed with a two's complement displacement integer d) is loaded into register r, where r identifies register A, B, C, D, E, H or L, assembled as follows in the object code:

#### Register r

A = 111

B = 000

C = 001

D = 010

E = 011

H = 100

L = 101

M CYCLES: 5 T STATES: 19(4,4,3,5,3) 4 MHZ E.T.: 4.75

Condition Bits Affected: None

#### Example:

If the Index Register IX contains the number 25AFH, the instruction